Data Sheet Rev. 1.0 April 2007

# 9.0-9.6 GHz Low Noise Amplifier

#### **Features**

- Frequency Range: 9-9.6 GHz

Low Noise Figure < 1.3 dB</li>

- ◆ 26.5 dB nominal gain

- ◆ 10 dBm P<sub>1dB</sub>

- + High IP3

- ◆ Input Return Loss > 12 dB

- ◆ Output Return Loss > 10 dB

- DC decoupled input and output

- ◆ 0.15 µm InGaAs pHEMT Technology

- ◆ Chip dimension: 3.0 x 3.0 x 0.1 mm

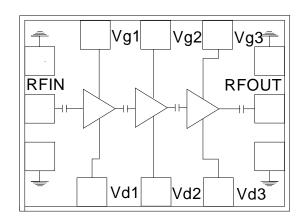

## **Functional Diagram**

#### **Typical Applications**

- RADAR

- Military

- Test Equipment and sensors

- ◆ Point-to-Point Radios, Point-to-Multi-Point Radios & VSATS

#### **Description**

The ASTRA 2142024 is a three stage ultra low noise amplifier that operates from 9.0-9.6 GHz. The LNA features 26.5 dB gain and has a typical mid-band noise figure of 1.3 dB. The LNA has nominal input return losses of 12 dB and output return loss of 10 dB. The nominal P1dB is 10 dBm.

Dual bias technique has been employed to facilitate gain control with gate bias. Circuit ground is provided through vias to backside metallization. The ASTRA 2142024 performs well as a low noise amplifier in receive applications and as a driver or buffer amplifier where high gain, excellent linearity and low power consumption are important.

## Absolute Maximum Ratings<sup>1</sup>

| Parameter               | Absolute Maximum | Units |

|-------------------------|------------------|-------|

| Drain bias voltage (Vd) | +6               | volts |

| RF input power          | +10              | dBm   |

| Operating temperature   | -50 to +85       | °C    |

| Storage Temperature     | -65 to +150      | °C    |

1. Operation beyond these limits may cause permanent damage to the component

Data Sheet Rev. 1.0 April 2007

# Electrical Specifications @ $T_A$ = 25 °C, $V_{d1}$ = $V_{d2}$ = $V_{d3}$ = 5V, Vg1=Vg2=Vg3=-0.3 to -0.5V, $Z_o$ =50 $\Omega$

| Parameter                                                              | Тур          | Units |

|------------------------------------------------------------------------|--------------|-------|

| Frequency Range                                                        | 9.0-9.6      | GHz   |

| Gain                                                                   | 26.5         | dB    |

| Gain Flatness                                                          | <u>+</u> 0.5 | dB    |

| Noise Figure                                                           | 1.3          | dB    |

| Input Return Loss                                                      | 12           | dB    |

| Output Return Loss                                                     | 10           | dB    |

| Output Power (P1dB)                                                    | +10          | dBm   |

| Saturated Output Power (Psat)                                          | +13          | dBm   |

| Output Third Order Intercept (IP3)                                     | 20           | dBm   |

| Supply Current (ld) (Vd1 = Vd2= Vd3 = 5V) (Vg1=Vg2=Vg3= -0.3 to -0.5V) | 75           | mA    |

#### Note:

1. Electrical performance from test fixture measurements

Email: <u>info@astramwp.com</u> URL: <u>www.astramtl.com</u>

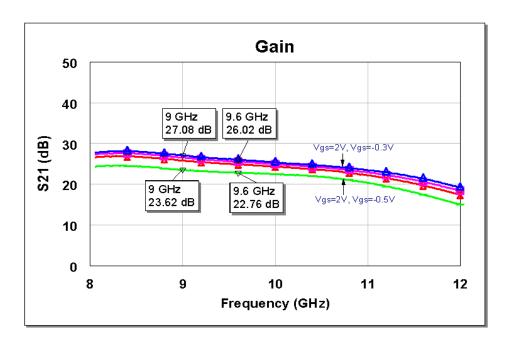

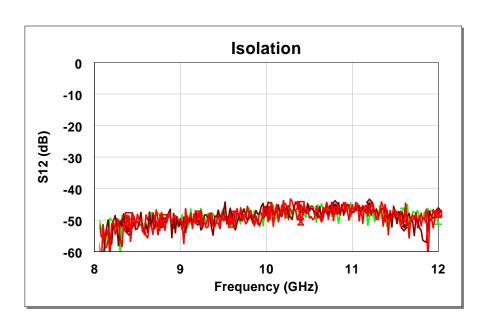

#### Test fixture data

Vd1=Vd2=Vd3=5V, Vg1=Vg2=Vg3=-0.3V to -0.5V. Total Current =75ma,  $T_A=25$  °C

## **Test fixture data**

Vd1=Vd2=Vd3=5V, Vg1=Vg2=Vg3=-0.3 to -0.5V. Total Current =75ma,  $T_A=25$  °C

Phone: +91-40-30618000 Fax: +91-40-30618048 Page 3 of 7 Email: info@astramwp.com URL: www.astramtl.com

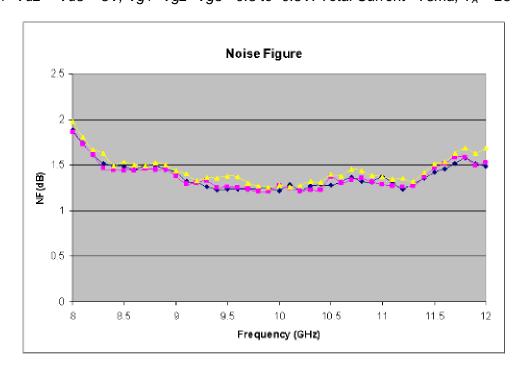

#### **Test fixture data**

Vd1=Vd2=Vd3=5V, Vg1=Vg2=Vg3=-0.3 to -0.5 V. Total Current =75ma,  $T_A=25$  °C

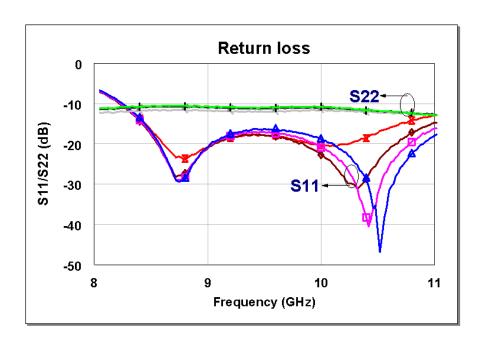

#### **Test fixture data**

Vd1=Vd2=Vd3=5V, Vg1=Vg2=Vg3=-0.3 to -0.5 V. Total Current =75ma,  $T_A$  =25 °C

Data Sheet Rev. 1.0 April 2007

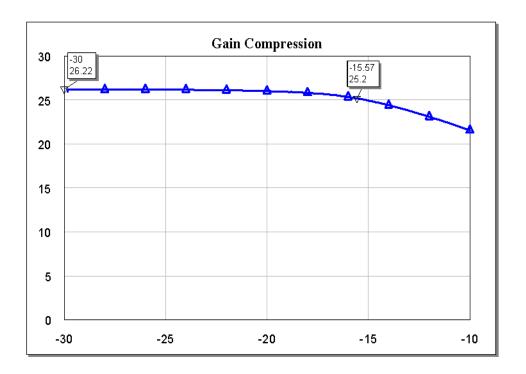

#### **Test fixture data**

Vd1=Vd2=Vd3=5V, Vg1=Vg2=Vg3=-0.3 V. Total Current =75ma,  $T_A$  =25 °C

Pout at 1 dB compression = 10 dBm@9 GHz

Phone: +91-40-30618000 Fax: +91-40-30618048 Page 5 of 7 Email: info@astramwp.com URL: www.astramtl.com

Data Sheet Rev. 1.0 April 2007

## **Mechanical Characteristics**

**Units: Millimeters [Inches]**

All RF and DC bond pads are 100µm x 100µm

#### Note:

Pad 1: RF in

Pad 2: VG1 (-0.3V to -0.5V) Pad 3: VG2 (-0.3V to -0.5V) Pad 4: VG3 (-0.3V to -0.5V)

Pad 5 : RFout Pad 6 : VD3 (5V) Pad 7 : VD2 (5V) Pad 8 : VD3 (5V)

Rev. 1.0 April 2007

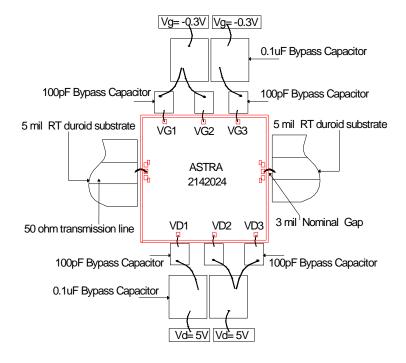

#### **Recommended Assembly Diagram**

#### Note:

- 1. Two 1 mil (0.0254mm) bond wires of minimum length should be used for RF input and output.

- 2. Two 1 mil (0.0254mm) bond wires of minimum length should be used from chip bond pad to 100pF capacitor.

- 3. Input and output 50 ohm lines are on 5 mil substrate.

- 0.1 μF capacitors may be additionally used as a second level of bypass for reliable operation.

Die attach: Use AuSn (80/20) 1-2 mil. Preform solder.

**Wire bonding:** For DC pad connections use either ball or wedge bonds. For best RF performance, use of 150 - 200µm length of wedge bonds is advised. Ball bonds are also acceptable.

GaAs MMIC devices are susceptible to Electrostatic discharge. Proper precautions should be observed during handling, assembly & testing

All information and Specifications are subject to change without prior notice