Data Sheet Rev. 1.0 November 2010

# 8 – 10 GHz 4 Watt Power Amplifier

## **Features**

- ◆ Frequency Range: 8 10GHz

- 36.5 dBm Psat

- ◆ 14 dB Power gain

- ◆ 25% PAE

- + High IP3

- Input Return Loss > 9 dB

- ◆ Output Return Loss > 9 dB

- Dual bias operation

- DC decoupled input and output

- ◆ 0.5 µm InGaAs pHEMT Technology

- Chip dimension: 5.3 x 2.8 x 0.1 mm

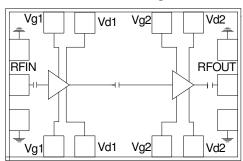

## **Functional Diagram**

# **Typical Applications**

- + RADAR

- Military & space

- LMDS, VSAT

# **Description**

The AMT2144091 is a X-band Power amplifier with 36.5dBm power output. The PA uses 2 stages of amplification and operates in 8 – 10 GHz frequency range. The PA features 14 dB of gain with input and output return losses of 9 dB respectively. The PA has a high IP3 of 45dBm and 25% PAE. This feature enables it to be used in the applications requiring efficiency along with linearity. The chip operates with dual bias supply voltage. The die is fabricated using a reliable 0.5µm InGaAs pHEMT technology. The Circuit grounds are provided through vias to the backside metallization.

# **Absolute Maximum Ratings** (1)

| Parameter                      | Absolute Maximum | Units |

|--------------------------------|------------------|-------|

| Drain bias voltage (Vd)        | +10              | volts |

| Drain current (Id)             | 2.3              | А     |

| RF input power (RFin at Vd=9V) | 33               | dBm   |

| Operating temperature          | -50 to +85       | °C    |

| Storage Temperature            | -65 to +150      | °C    |

1. Operation beyond these limits may cause permanent damage to the component

Rev. 1.0 November 2010

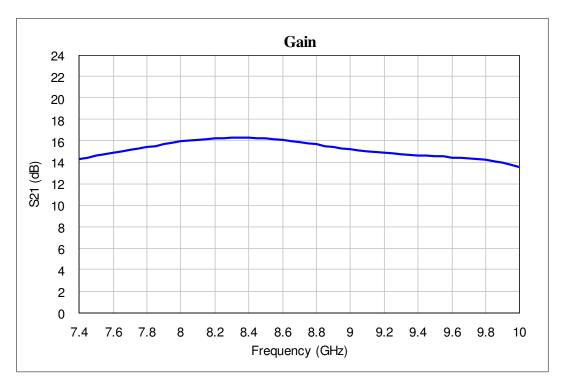

# Electrical Specifications $^{(1)}$ @ $T_A$ = 25 °C, $V_{d1}$ = $V_{d2}$ = 8V, $V_{g1}$ = $V_{g2}$ = -1.1V $Z_o$ =50 $\Omega$

| Parameter                                       | Тур.   | Units |

|-------------------------------------------------|--------|-------|

| Frequency Range                                 | 8 – 10 | GHz   |

| Gain                                            | 14     | dB    |

| Gain Flatness                                   | +/-1   | dB    |

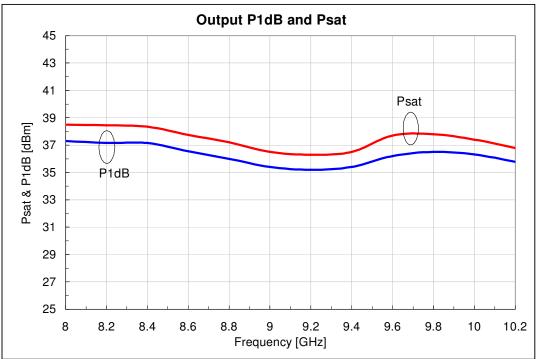

| Output Power (P1 dB)                            | 35.5   | dBm   |

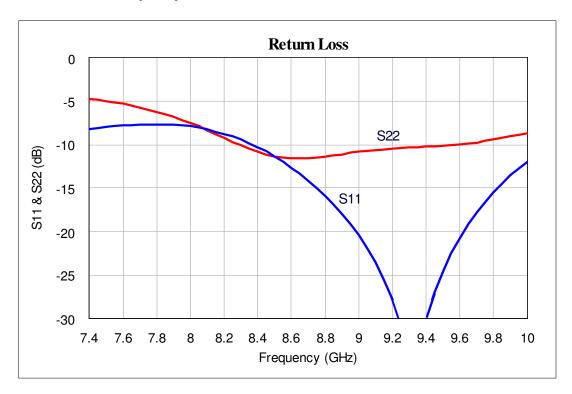

| Input Return Loss                               | 9      | dB    |

| Output Return Loss                              | 9      | dB    |

| Saturated output power (Psat)                   | 36.5   | dBm   |

| Output Third Order Intercept (IP3)              | 45     | dBm   |

| Power Added Efficiency (PAE)                    | 25%    |       |

| Supply Current(I <sub>dq</sub> )                | 1.5    | А     |

| Supply Current(I <sub>dsat</sub> <sup>2</sup> ) | 2.1    | А     |

#### Note:

- 1. Electrical specifications as measured in test fixture.

- 2. I<sub>dsat</sub> is the maximum drain current under input RF drive condition.

Rev. 1.0 November 2010

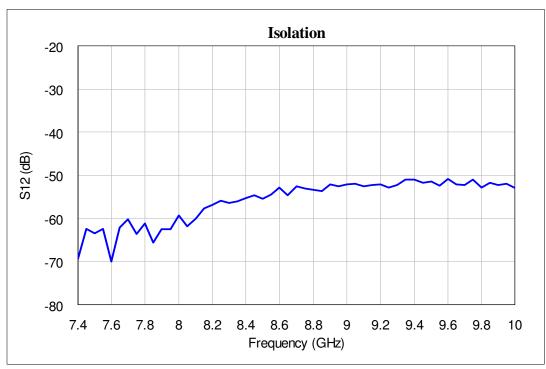

# **Test fixture data**

$V_{d1}=V_{d2}=8V,\ V_{g1}=V_{g2}=-1.1V,\ Total\ Current\ (Idq)=1.5A,\ T_A=25\ ^{\circ}C$

## **Test fixture data**

$$V_{d1} = V_{d2} = 8V$$

,  $V_{g1} = V_{g2} = -1.1V$ , Total Current (ldq) = 1.5A,  $T_A = 25$  °C

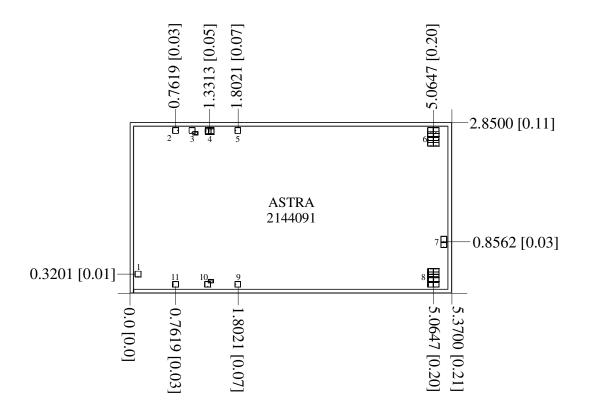

# **Bond Pad Locations**

Units: millimeters (inches)

#### Note:

1. All RF and DC bond pads are 100μm x 100μm

2. Pad no. 1 : RF IN

3. Pad no. 2,11 : 1st stage gate  $voltage(V_{g1})$

4. Pad no. 7 : RF Output

5. Pad no. 4 :  $1^{st}$  stage drain voltage( $V_{d1}$ )

6. Pad no. 5,9 :  $2^{nd}$  stage gate voltage( $V_{g2}$ )

7. Pad no. 6,8 :  $2^{nd}$  stage drain voltage ( $V_{d2}$ )

8. All the dimensions shown above are measured taking bottom left corner as reference.

Rev. 1.0 November 2010

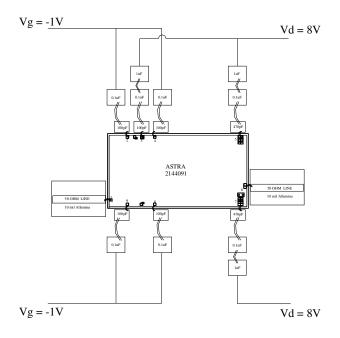

# **Recommended Assembly Diagram**

#### Note:

- 1. Open stub of 4mm length, 0.7mm width and 0.1mm thickness to be placed at output immediate to the chip for proper matching.

- 2. Two 1 mil (0.0254mm) bond wires of minimum length should be used for RF input and output.

- 3. Two 1 mil (0.0254mm) bond wires of minimum length should be used from chip bond pad to 100pF capacitor.

- 4. Input and output 50 ohm lines are on 10 mil Allumina or 5 mil RT Duroid.

- 5. 100pF,0.1uF and 1uF bypass capacitors are used as shown above.

- 6. The RF input & output ports are DC decoupled on-chip.

**Die attach:** For Epoxy attachment, use of a two-component conductive epoxy is recommended. An epoxy fillet should be visible around the total die periphery. If Eutectic attachment is preferred, use of fluxless AuSn (80/20) 1-2 mil thick preform solder is recommended. Use of AuGe preform should be strictly avoided.

Wire bonding: For DC pad connections use either ball or wedge bonds. For best RF performance, use of 150 - 200μm length of wedge bonds is advised. Single Ball bonds of 250-300μm though acceptable, may cause a deviation in RF performance.

GaAs MMIC devices are susceptible to Electrostatic discharge. Proper precautions should be observed during handling, assembly & testing

All information and Specifications are subject to change without prior notice